Jerarquía de memoria

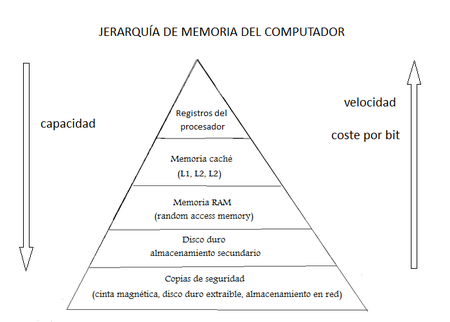

La jerarquía de memoria es la organización piramidal de la memoria en niveles que tienen las computadoras.

El objetivo es acercarse el rendimiento de una memoria de gran velocidad al coste de una memoria de baja velocidad, basándose en el principio de cercanía de referencias.[1]

Puntos básicos[editar]

Los puntos básicos relacionados con la memoria pueden resumirse en:

- Capacidad

- Velocidad

- Coste por bit

La cuestión de la capacidad es simple, cuanto más memoria haya disponible, más podrá utilizarse.

La velocidad óptima para la memoria es la velocidad a la que el microprocesador puede trabajar, de modo que no haya tiempos de espera entre cálculo y cálculo, utilizados para traer operandos o guardar resultados.

En suma, el coste de la memoria no debe ser excesivo, para que sea factible construir un equipo accesible.

Los tres factores compiten entre sí, por lo que hay que encontrar un equilibrio.

Las siguientes afirmaciones son válidas:

- A menor tiempo de acceso mayor coste.

- A mayor capacidad menor coste por bit.

- A mayor capacidad menor velocidad.

Se busca entonces contar con capacidad suficiente de memoria, con una velocidad que sirva para satisfacer la demanda de rendimiento y con un coste que no sea excesivo.

Gracias a un principio llamado cercanía de referencias, es factible utilizar una mezcla de los distintos tipos y lograr un rendimiento cercano al de la memoria más rápida.

Niveles jerárquicos[editar]

Los niveles

- Nivel 0: Registro

- Nivel 1: Memoria caché

- Nivel 2: Memoria primaria (RAM)

- Nivel 3: Disco duro (con el mecanismo de memoria virtual)

- Nivel 4: Cintas magnéticas (consideradas las más lentas, con mayor capacidad, de acceso secuencial)

Gestión de memoria[editar]

Los lenguajes de programación actuales generalmente asumen la existencia de únicamente dos niveles de memoria: memoria primaria y memoria secundaria (normalmente en disco). En lenguaje ensamblador, ensamblador en línea, y lenguajes como C y C++, se pueden direccionar datos directamente a los registros de la CPU.

- Programadores: deben ser responsables del movimiento entre memoria principal y disco mediante el uso de ficheros.

- Hardware: el movimiento de datos entre la memoria principal y los niveles de caché es realizado por algoritmos de hardware.

- Compiladores: son responsables de optimizar el código de modo que el uso de los registros y la caché sea eficiente.

Véase también[editar]

Referencias[editar]

- ↑ Database System Concepts (capítulo 10). Abraham Silberschatz, Hank Korth y S. Sudarshan. 7ª edición (2019). McGraw-Hill